Product Summary

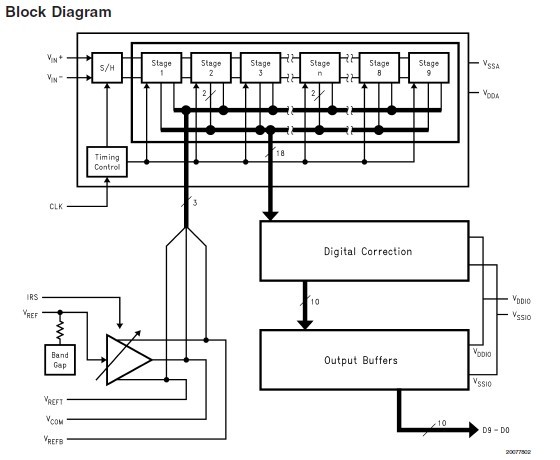

The ADC10040CIMT is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 10-bit digital words at 40 Megasamples per second (MSPS). This ADC10040CIMT uses a differential, pipeline architecture with digital error correction and an on-chip sample-and-hold circuit to provide a complete conversion solution, and to minimize power consumption, while providing excellent dynamic performance. A unique sample-and-hold stage yields a fullpower bandwidth of 400 MHz. Operating on a single 3.0V power supply, the ADC10040CIMT consumes just 55.5 mW at 40 MSPS, including the reference current. The Standby feature reduces power consumption to just 13.5 mW.

Parametrics

ADC10040CIMT absolute maximum ratings: (1)Resolution 10 Bits; (2)Conversion Rate 40 MSPS; (3)Full Power Bandwidth 400 MHz; (4)DNL ±0.3 LSB (typ); (5)SNR (fIN = 11 MHz) 59.6 dB (typ); (6)SFDR (fIN = 11 MHz) -80 dB (typ); (7)Data Latency 6 Clock Cycles; (8)Supply Voltage +3.0V; (9)Power Consumption, 40MHz 55.5mW.

Features

ADC10040CIMT features: (1)Single +3.0V operation; (2)Selectable 2.0 VP-P, 1.5 VP-P, or 1.0 VP-P full-scale input swing; (3)400 MHz -3 dB input bandwidth; (4)Low power consumption; (5)Standby mode; (6)On-chip reference and sample-and-hold amplifier; (7)Offset binary or two’s complement data format; (8)Separate adjustable output driver supply to accommodate 2.5V and 3.3V logic families; (9)28-pin TSSOP package.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

ADC10040CIMT |

National Semiconductor (TI) |

ADC (A/D Converters) |

Data Sheet |

|

|

||||||||||||

|

ADC10040CIMT/NOPB |

National Semiconductor (TI) |

ADC (A/D Converters) |

Data Sheet |

|

|

||||||||||||

|

ADC10040CIMTX/NOPB |

National Semiconductor (TI) |

ADC (A/D Converters) |

Data Sheet |

|

|

||||||||||||

|

ADC10040CIMTX |

National Semiconductor (TI) |

ADC (A/D Converters) |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))