Product Summary

The XC3042APQ100-7I is a Logic Cell Array. It offers the following enhancements over the popular XC3000 family. The CLB Clock Enable input of the XC3042APQ100-7I can be driven from a second vertical Longline. These two additions result in more efficient and faster designs when horizontal Longlines are used for data bussing.

Parametrics

XC3042APQ100-7I absolute maximum ratings: (1)Supply voltage relative to GND: –0.5 to +7.0 V; (2)Input voltage with respect to GND: –0.5 to VCC +0.5 V; (3)Voltage applied to 3-state output: –0.5 to VCC +0.5 V; (4)Storage temperature (ambient): –65 to +150 ℃; (5)Maximum soldering temperature (10 s @ 1/16 in.): +260 ℃; (6)Junction temperature plastic: +125 ℃; (7)Junction temperature ceramic: +150 ℃.

Features

XC3042APQ100-7I features: (1)Enhanced, high performance FPGA family with five device types: Improved redesign of the basic XC3000 LCA; (2)Family, Logic densities from 1,000 to 6,000 gates; (3)Superset of the industry-leading XC3000 family: Identical to the basic XC3000 in structure, pin out, design methodology, and software tools; (4)Additional programmable interconnection points (PIPs): Improved access to longlines and CLB clock enable inputs, Most efficient XC3000-class solution to bus-oriented designs.

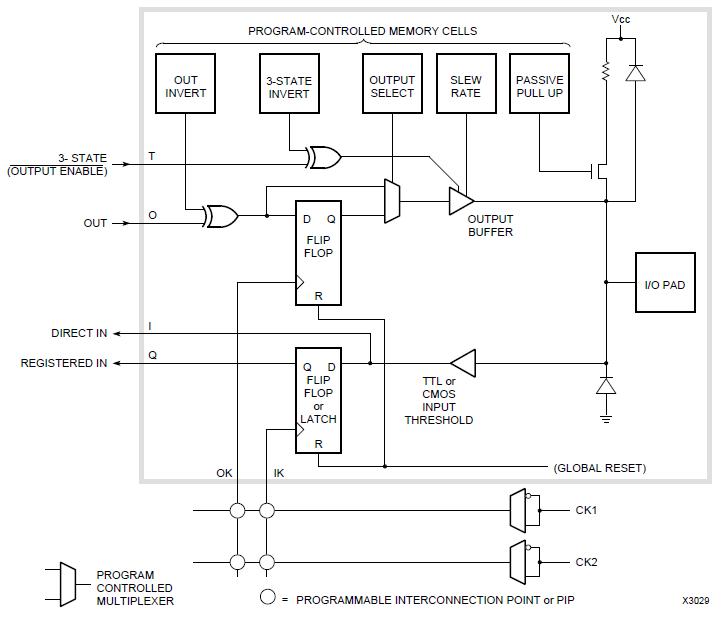

Diagrams

|

XC3000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC3000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC3000L |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC3020A-7PC84C |

|

IC LOGIC CL ARRAY 2000GAT 84PLCC |

Data Sheet |

Negotiable |

|

||||

|

XC3030-100PC44C |

|

IC LOGIC CL ARRAY 3000GAT 44PLCC |

Data Sheet |

Negotiable |

|

||||

|

XC3030-100PC68C |

|

IC LOGIC CL ARRAY 3000GAT 68PLCC |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))